2023 BUAA CO review: P0

课下提交

Q1 P0_L0_CRC(题目编号1119-13)

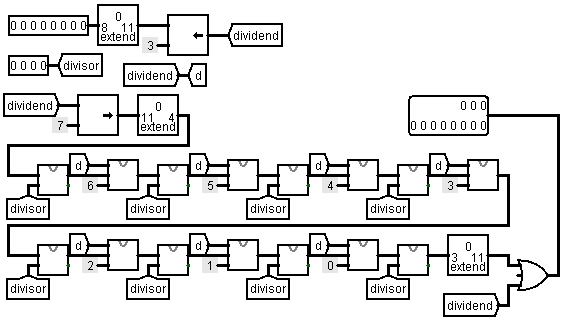

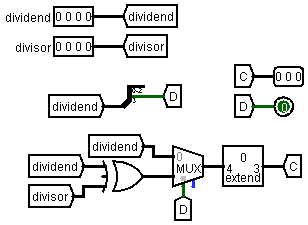

使用Logisim搭建一个除数为四位,原数据帧为8位的CRC校验码计算电路。具体模块端口定义如下:

| 信号名 | 方向 | 描述 |

|---|---|---|

| A[7:0] | I | 8位原数据帧 |

| B[3:0] | I | 4位除数 |

| C[10:0] | O | 8位原数据帧 + 3位校验码 |

- 文件内模块名:CRC

- 规定除数的最高位一定为1,不必考虑非1的情况

关于CRC校验码,可以看看这位大佬的总结

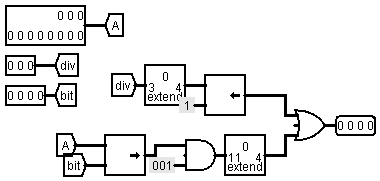

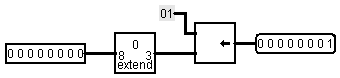

- 由题意,需要进行8次四位模二除法,每次将上一次的余数输出,

拼接一位被除数作为下一次四位模二除法的被除数输入 - 对于四位模二除法,若被除数最高位为1,则商为1,余数为被除数与除数异或

若最高位为0,则商为0,余数直接等于被除数

Q2 P0_L0_GRF(1119-269)

使用logisim搭建一个GRF。GRF中包含32个32位寄存器,分别对应0~31号寄存器,其中0号寄存器读取的结果恒为0。具体模块端口定义如下:

| 信号名 | 方向 | 描述 |

|---|---|---|

| clk | I | 时钟信号 |

| reset | I | 复位信号,将32个寄存器中的值全部清零 1: 复位 0: 无效 |

| WE | I | 写使能信号 1: 可向GRF中写入数据 0: 不能向GRF中写入数据 |

| A1 | I | 5位地址输入信号,指定32个寄存器中的一个,将其中储存的数据读出到RD1 |

| A2 | I | 5位地址输入信号,指定32个寄存器中的一个,将其中储存的数据读出到RD2 |

| A3 | I | 5位地址输入信号,指定32个寄存器中的一个,作为写入的目标寄存器 |

| WD | I | 32位数据输入信号 |

| RD1 | O | 输出A1指定的寄存器中的32位数据 |

| RD2 | O | 输出A2指定的寄存器中的32位数据 |

模块功能定义如下:

| 序号 | 功能名称 | 描述 |

|---|---|---|

| 1 | 复位 | reset信号有效时,所有的寄存器储存的数值清零,其行为与logisim自带部件的reset接口完全相同 |

| 2 | 读数据 | 读出A1,A2地址对应寄存器中所储存的数据到RD1,RD2 |

| 3 | 写数据 | 当WE有效且时钟上升沿来临时,将WD写入A3对应的寄存器中 |

- 0号寄存器读出的数据在任何时刻 都为0

- 文件内模块名:grf

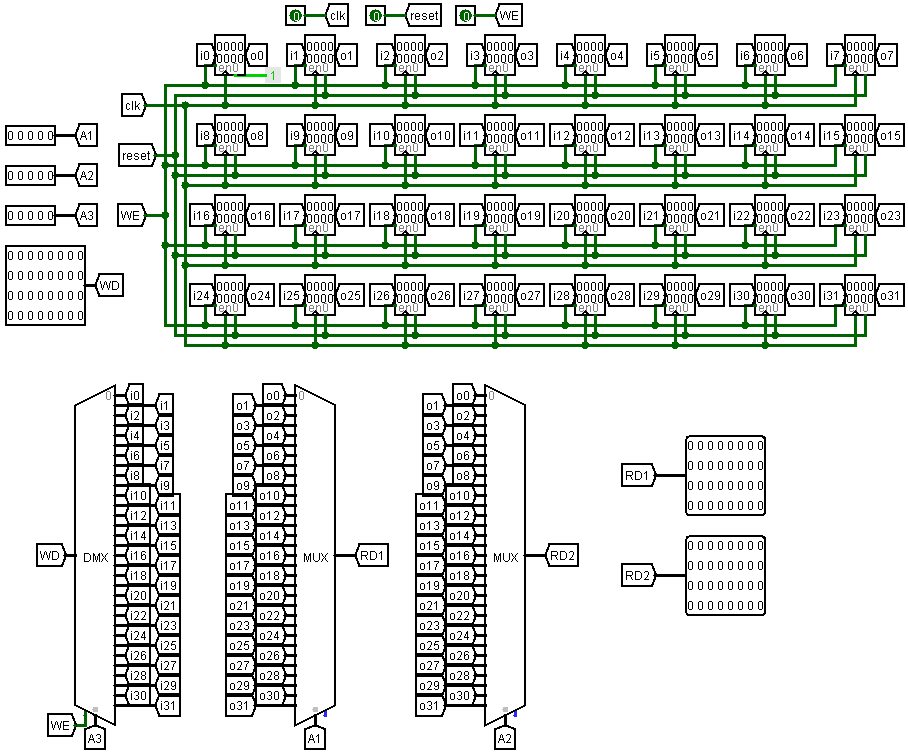

- 由题目的要求可知,在根据的值将数据写入对应寄存器的同时,还需要保持其他寄存器不变

方法一:

- 32个寄存器,每个输入端口接上对应的Tunnel,Tunnel到一个DMX上

- 将DMX的

Three-state属性设置为Yes,Disabled Output属性设置为Floating。这样,DMX使能时,除选中的输出为输入值外,其余输出均为浮空值(高阻态x);不使能时,所有输出都为x。而Register在输入端为x时不更新,故满足题目需求。

方法二:

- 每个寄存器

Enable端接上对应的Tunnel,Tunnel到一个Deco上 - 将Deco的

Three-state属性设置为Yes,Disabled Output属性设置为Zero。(Register在Enable端为x时依然会使能)

- 最后注意0号寄存器,可以不设置输出,也可以设置

reset为常量1

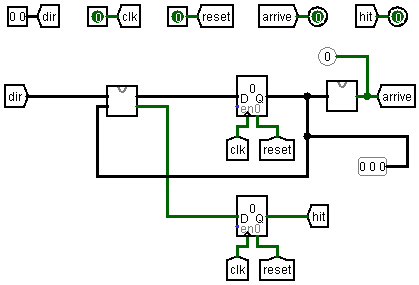

Q3 P0_L1_navigation_2020(1119-393)

用logisim搭建一个可以导航的Moore型有限状态机,通过输入序列判断是否到达B

- 题目要求:

- 只能往东南西北四个方向行走,且若能行走,则每次只能行走一格。若下一步>撞墙,则将hit置高一周期并保持原地不动,等待下一周期再进行运动。(若下一步不会撞墙,则继续行进,hit在此周期置0)

- 走到B机房后,“到达”信号需要置位,并保持一周期。到达B机房后计小组将会在下一周期回到原点,(下一周期的输入将被忽略掉)等待下下周期的输入,继续测试他的序列。

- 计小组在时钟上升沿的时候就已经知道自己下一步的方向并且瞬移过去,并且立即做出判断。

- 端口定义:

| 信号名 | 方向 | 描述 |

|---|---|---|

| dir[1:0] | I | 表示行走的方向 00:向北走 01:向东走 10:向南走 11:向西走 |

| clk | I | 时钟信号 |

| reset | I | 异步复位信号 |

| arrive | O | 是否到达 |

| hit | O | 是否撞上墙壁 |

- 模块名:navigation

画出状态转移图

然后根据转移表Analyze Circuit即可

只展示模块

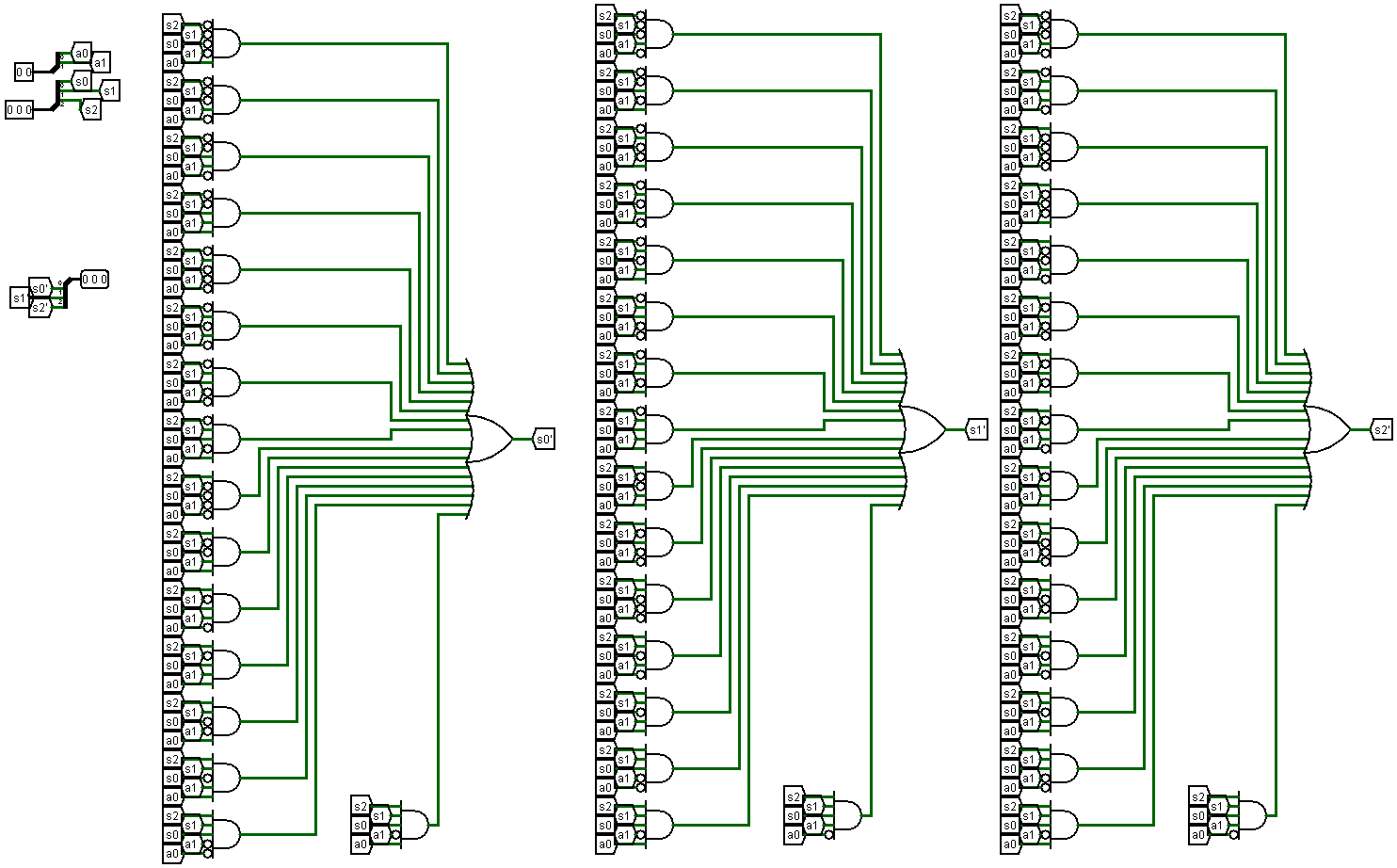

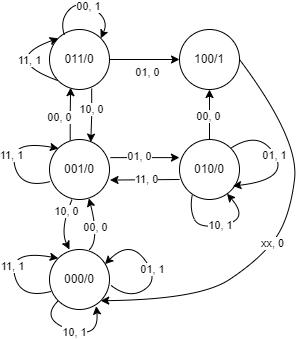

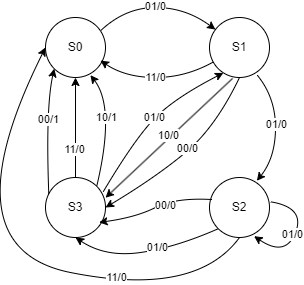

Q4 P0_L0_FSM(1119-9)

使用Logisim搭建一个Mealy型有限状态机 检测串行输入字符串中的能匹配正则表达式b{1,2}[ac]{2}的子串并输出。具体模块端口定义如下:

| 信号名 | 方向 | 描述 |

|---|---|---|

| In[1:0] | I | 串行方式输入字符串 规定 00 表示 ‘a’,01 表示 ‘b’,10 表示 ‘c’,11 表示其他字符 |

| CLR | I | 清除置位信号 |

| Z | O | 输出是否检测到了与表达式匹配的子串 1:检测到了 0:未检测到 |

- 文件内模块名:fsm

- 注意:每当匹配到一个子串时,需要输出一次1。例如对字符串bacbacac,模块应当在第1个c输入和第2个c输入时输出1,而在其他时刻保持输出为0。

- 注意:有限状态机的设计是Mealy 型有限状态机。

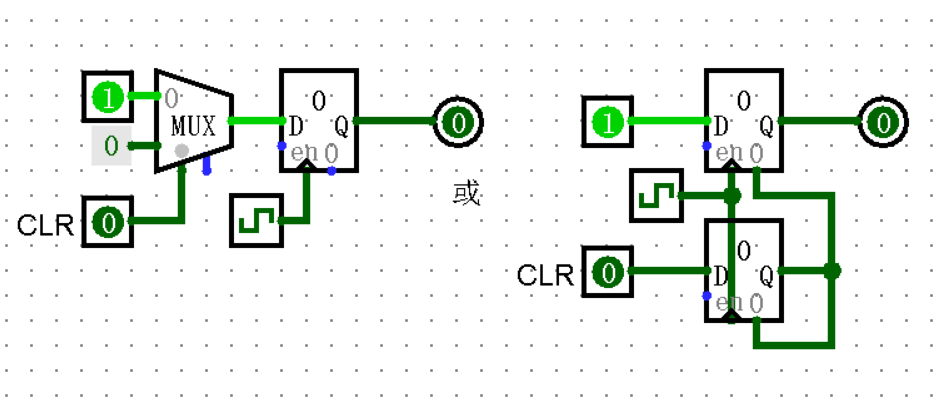

- 要求同步复位

- 定义4个状态:

| S0 | S1 | S2 | S3 |

|---|---|---|---|

| 检测到null | 检测到b | 检测到bb | 检测到b{1,2}[ac] |

- 转移图为:

- 同步复位方法:

附加题Q1 P0_L1_ftoi(1119-319)

使用Logisim进行组合逻辑设计,要求输入一个16位的单精度浮点数(符合IEEE-754标准),输出该浮点数的整数部分(包含符号),用32位二进制符号数表示。

IEEE-754 标准中一个半精度16位浮点数的表示方法:

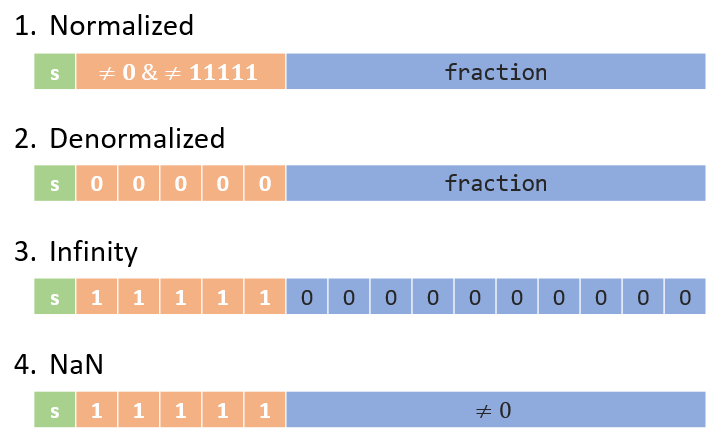

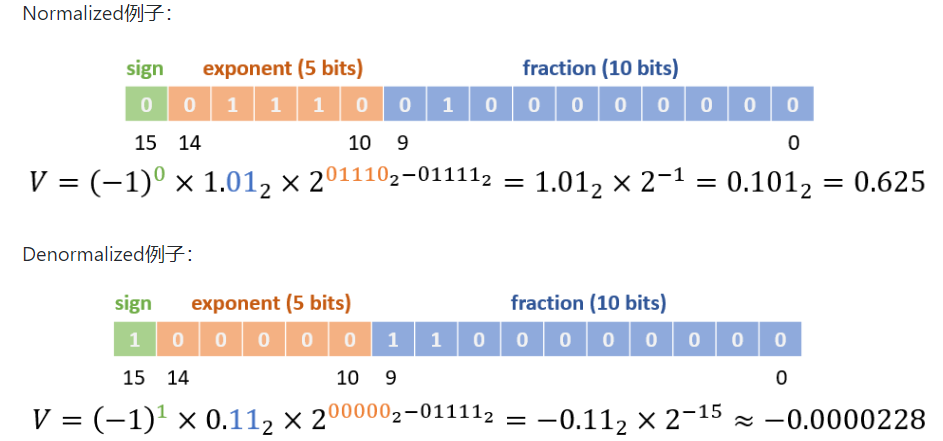

利用这种浮点数表示方法进行编码后的值可以分为4类,如下图所示

- S代表最高位符号位,由sign[15]位编码,规定S=sign

- E代表指数,由图中exponent[14:10]域编码,规定补码

- M代表小数点后的二进制小数位,由图中frac[9:0]域编码,Normalized的情况M永远有一位前导1,因此不占位,相当于1 + frac;而Denormalized的情况frac前面是0,M默认就是frac,即规定

模块端口定义如下:

| 信号名 | 方向 | 描述 |

|---|---|---|

| float[15:0] | I | 16位半精度浮点数(IEEE-754标准) |

| int[31:0] | O | 该浮点数的整数部分(带符号),用32位符号数的补码来表示,超出表示范围则取低32位。第3类Infinity和第4类NaN为了简化直接输出0即可 |

- 文件内模块名: ftoi

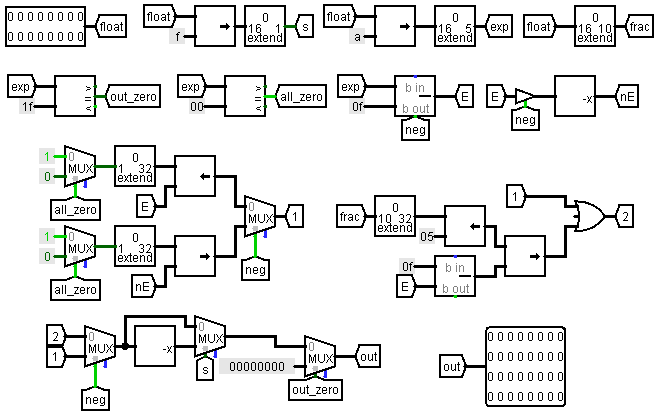

- 由题意,只需计算型的整数部分

- 先取出

sign和exponent进行判断,然后根据exponent是否小于0x0f继续分类(可使用和进行处理) - 根据不同的情况对

fraction进行移位即可

建得有点乱

课上考试

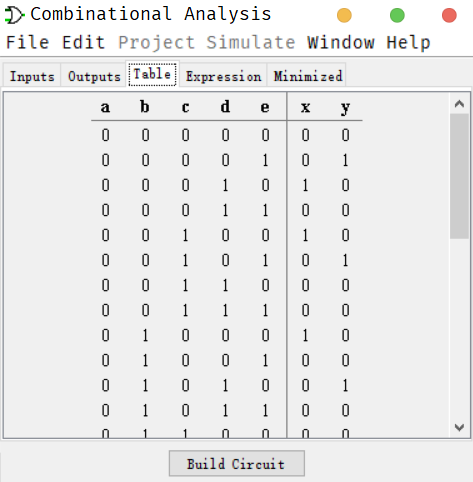

Q1 P0_L2_nonexist_2023(1120-1149)

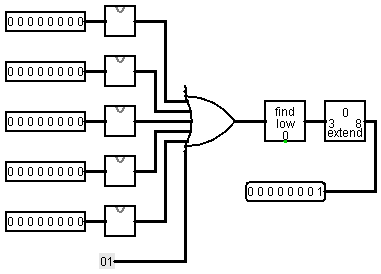

使用 Logisim 搭建一个组合电路。给定输入的 5 个任意无符号二进制数。确定输入中未出现的最小正整数是多少。

模块端口定义如下:

| 名称 | 功能 | 位宽 | 方向 |

|---|---|---|---|

| input1 | 数据输入 | 8 | I |

| input2 | 数据输入 | 8 | I |

| input3 | 数据输入 | 8 | I |

| input4 | 数据输入 | 8 | I |

| input5 | 数据输入 | 8 | I |

| 输出 | 结果 | 8 | O |

- 显然,本题的答案是1-6中未出现的最小正整数

- 于是可以用独热码的方式记录这六个数有哪些出现过,再用找出最低位0即可

- 最后记得调整

appearance(

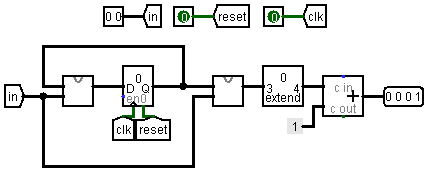

Q2 P0_L3_walker_2023(1120-1158)

设计Mealy型状态机模拟在回型建筑中移动的学生。

某校有一栋回字型的建筑,可以分为八个单元,由右上角起顺时针编号为 1 至 8,结成一个环。现一名学生从编号 1(东北角)的单元开始移动。

- 当学生恰好移动向相邻单元方向时,学生进入该相邻单元,输出其编号。

- 当学生的移动方向上没有单元,这次不移动,直接输出当前所在单元格编号。

输入输出如下:

- 输入

00时,学生试图向上(北)移动。 - 输入

01时,学生试图向下(南)移动。 - 输入

10时,学生试图向左(西)移动。 - 输入

11时,学生试图向右(东)移动。 - 输出学生试图移动到的建筑单元。

模块端口定义如下:

| 名称 | 功能 | 位宽 | 方向 |

|---|---|---|---|

| input | 方向输入 | 2 | I |

| reset | 异步复位信号 | 1 | I |

| clk | 时钟信号 | 1 | I |

| output | 结果 | 4 | O |

- 可以用0-7来表示8个房间,这样只需用3位就可以存下状态,最后再加1即可

- 同时由于本体状态只会进行

-1和+1两种变化,故可以用S0,S1,S2分别表示不动、进一步、退一步,这样又减去一位状态

Q3 P0_L5_hexcode_2023

题意

使用 Logisim 搭建一个 Moore 状态机。该状态机每周期输入四位二进制数,作为一位十六进制输入。当此前三个周期的输入恰好为三个特定序列之一时,输出对应序列编号。

- 对于输入与下列三者均不一致的情况,输出

0 - 对于输入依次为

EEE的情况,输出1 - 对于输入依次为

A0E的情况,输出2 - 对于输入依次为

0A0的情况,输出3

模块端口定义如下:

| 名称 | 功能 | 位宽 | 方向 |

|---|---|---|---|

| input | 十六进制输入 | 4 | I |

| reset | 异步复位信号 | 1 | I |

| clk | 时钟信号 | 1 | I |

| output | 识别结果 | 2 | O |

题解

法一:

用一个10个状态的自动机来描述字符之间的转换关系

组合逻辑分析点错直接rmk

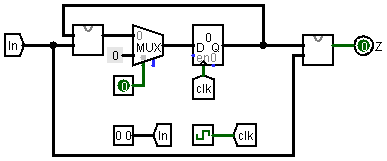

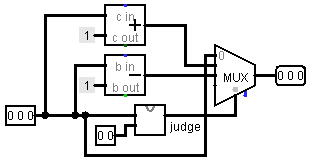

法二:

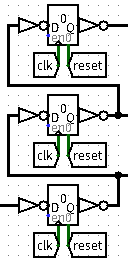

- 可以用三个串联的寄存器,依次将三个周期的输出的存下来(类比移位寄存器)

- 然后判断答案就十分简单了,可以组合逻辑也可以直接用

- 需要注意的是,寄存器初始值为0,所以为了避免误判

0A0的情况,可以这样设计:

总结

考试之前不知道有Analyze Circuit这个功能,考场上直接手搓与或门,结果第二题我那个做法一直没查出来错,最后卡点搓了个这个东西出来极限通过